ਦਾ ਡਿਜ਼ਾਈਨਫੋਟੋਨਿਕਏਕੀਕ੍ਰਿਤ ਸਰਕਟ

ਫੋਟੋਨਿਕ ਏਕੀਕ੍ਰਿਤ ਸਰਕਟ(PIC) ਅਕਸਰ ਗਣਿਤਿਕ ਲਿਪੀਆਂ ਦੀ ਮਦਦ ਨਾਲ ਤਿਆਰ ਕੀਤੇ ਜਾਂਦੇ ਹਨ ਕਿਉਂਕਿ ਇੰਟਰਫੇਰੋਮੀਟਰਾਂ ਜਾਂ ਹੋਰ ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ ਮਾਰਗ ਦੀ ਲੰਬਾਈ ਦੀ ਮਹੱਤਤਾ ਹੁੰਦੀ ਹੈ ਜੋ ਮਾਰਗ ਦੀ ਲੰਬਾਈ ਪ੍ਰਤੀ ਸੰਵੇਦਨਸ਼ੀਲ ਹੁੰਦੇ ਹਨ।ਤਸਵੀਰਇਹ ਇੱਕ ਵੇਫਰ 'ਤੇ ਕਈ ਪਰਤਾਂ (ਆਮ ਤੌਰ 'ਤੇ 10 ਤੋਂ 30) ਨੂੰ ਪੈਟਰ ਕਰਕੇ ਤਿਆਰ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਜੋ ਕਿ ਕਈ ਬਹੁਭੁਜ ਆਕਾਰਾਂ ਤੋਂ ਬਣੀਆਂ ਹੁੰਦੀਆਂ ਹਨ, ਜੋ ਅਕਸਰ GDSII ਫਾਰਮੈਟ ਵਿੱਚ ਦਰਸਾਈਆਂ ਜਾਂਦੀਆਂ ਹਨ। ਫੋਟੋਮਾਸਕ ਨਿਰਮਾਤਾ ਨੂੰ ਫਾਈਲ ਭੇਜਣ ਤੋਂ ਪਹਿਲਾਂ, ਡਿਜ਼ਾਈਨ ਦੀ ਸ਼ੁੱਧਤਾ ਦੀ ਪੁਸ਼ਟੀ ਕਰਨ ਲਈ PIC ਦੀ ਨਕਲ ਕਰਨ ਦੇ ਯੋਗ ਹੋਣਾ ਬਹੁਤ ਜ਼ਰੂਰੀ ਹੈ। ਸਿਮੂਲੇਸ਼ਨ ਨੂੰ ਕਈ ਪੱਧਰਾਂ ਵਿੱਚ ਵੰਡਿਆ ਗਿਆ ਹੈ: ਸਭ ਤੋਂ ਨੀਵਾਂ ਪੱਧਰ ਤਿੰਨ-ਅਯਾਮੀ ਇਲੈਕਟ੍ਰੋਮੈਗਨੈਟਿਕ (EM) ਸਿਮੂਲੇਸ਼ਨ ਹੈ, ਜਿੱਥੇ ਸਿਮੂਲੇਸ਼ਨ ਉਪ-ਤਰੰਗ-ਲੰਬਾਈ ਪੱਧਰ 'ਤੇ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਹਾਲਾਂਕਿ ਸਮੱਗਰੀ ਵਿੱਚ ਪਰਮਾਣੂਆਂ ਵਿਚਕਾਰ ਪਰਸਪਰ ਪ੍ਰਭਾਵ ਮੈਕਰੋਸਕੋਪਿਕ ਪੈਮਾਨੇ 'ਤੇ ਸੰਭਾਲਿਆ ਜਾਂਦਾ ਹੈ। ਆਮ ਤਰੀਕਿਆਂ ਵਿੱਚ ਤਿੰਨ-ਅਯਾਮੀ ਸੀਮਤ-ਅੰਤਰ ਸਮਾਂ-ਡੋਮੇਨ (3D FDTD) ਅਤੇ ਈਜੇਨਮੋਡ ਵਿਸਥਾਰ (EME) ਸ਼ਾਮਲ ਹਨ। ਇਹ ਤਰੀਕੇ ਸਭ ਤੋਂ ਸਹੀ ਹਨ, ਪਰ ਪੂਰੇ PIC ਸਿਮੂਲੇਸ਼ਨ ਸਮੇਂ ਲਈ ਅਵਿਵਹਾਰਕ ਹਨ। ਅਗਲਾ ਪੱਧਰ 2.5-ਅਯਾਮੀ EM ਸਿਮੂਲੇਸ਼ਨ ਹੈ, ਜਿਵੇਂ ਕਿ ਸੀਮਤ-ਅੰਤਰ ਬੀਮ ਪ੍ਰਸਾਰ (FD-BPM)। ਇਹ ਤਰੀਕੇ ਬਹੁਤ ਤੇਜ਼ ਹਨ, ਪਰ ਕੁਝ ਸ਼ੁੱਧਤਾ ਦੀ ਕੁਰਬਾਨੀ ਦਿੰਦੇ ਹਨ ਅਤੇ ਸਿਰਫ ਪੈਰਾਕਸ਼ੀਅਲ ਪ੍ਰਸਾਰ ਨੂੰ ਸੰਭਾਲ ਸਕਦੇ ਹਨ ਅਤੇ ਉਦਾਹਰਣ ਵਜੋਂ, ਰੈਜ਼ੋਨੇਟਰਾਂ ਦੀ ਨਕਲ ਕਰਨ ਲਈ ਨਹੀਂ ਵਰਤੇ ਜਾ ਸਕਦੇ। ਅਗਲਾ ਪੱਧਰ 2D EM ਸਿਮੂਲੇਸ਼ਨ ਹੈ, ਜਿਵੇਂ ਕਿ 2D FDTD ਅਤੇ 2D BPM। ਇਹ ਤੇਜ਼ ਵੀ ਹਨ, ਪਰ ਸੀਮਤ ਕਾਰਜਸ਼ੀਲਤਾ ਰੱਖਦੇ ਹਨ, ਜਿਵੇਂ ਕਿ ਇਹ ਪੋਲਰਾਈਜ਼ੇਸ਼ਨ ਰੋਟੇਟਰਾਂ ਦੀ ਨਕਲ ਨਹੀਂ ਕਰ ਸਕਦੇ। ਇੱਕ ਹੋਰ ਪੱਧਰ ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਅਤੇ/ਜਾਂ ਸਕੈਟਰਿੰਗ ਮੈਟ੍ਰਿਕਸ ਸਿਮੂਲੇਸ਼ਨ ਹੈ। ਹਰੇਕ ਮੁੱਖ ਹਿੱਸੇ ਨੂੰ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਵਾਲੇ ਇੱਕ ਹਿੱਸੇ ਵਿੱਚ ਘਟਾ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਜੁੜਿਆ ਵੇਵਗਾਈਡ ਇੱਕ ਫੇਜ਼ ਸ਼ਿਫਟ ਅਤੇ ਐਟੇਨਿਊਏਸ਼ਨ ਤੱਤ ਵਿੱਚ ਘਟਾ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ। ਇਹ ਸਿਮੂਲੇਸ਼ਨ ਬਹੁਤ ਤੇਜ਼ ਹਨ। ਆਉਟਪੁੱਟ ਸਿਗਨਲ ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਮੈਟ੍ਰਿਕਸ ਨੂੰ ਇਨਪੁਟ ਸਿਗਨਲ ਨਾਲ ਗੁਣਾ ਕਰਕੇ ਪ੍ਰਾਪਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਸਕੈਟਰਿੰਗ ਮੈਟ੍ਰਿਕਸ (ਜਿਸਦੇ ਤੱਤ S-ਪੈਰਾਮੀਟਰ ਕਹਾਉਂਦੇ ਹਨ) ਕੰਪੋਨੈਂਟ ਦੇ ਦੂਜੇ ਪਾਸੇ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਸਿਗਨਲਾਂ ਨੂੰ ਲੱਭਣ ਲਈ ਇੱਕ ਪਾਸੇ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਸਿਗਨਲਾਂ ਨੂੰ ਗੁਣਾ ਕਰਦਾ ਹੈ। ਅਸਲ ਵਿੱਚ, ਸਕੈਟਰਿੰਗ ਮੈਟ੍ਰਿਕਸ ਵਿੱਚ ਤੱਤ ਦੇ ਅੰਦਰ ਪ੍ਰਤੀਬਿੰਬ ਹੁੰਦਾ ਹੈ। ਸਕੈਟਰਿੰਗ ਮੈਟ੍ਰਿਕਸ ਆਮ ਤੌਰ 'ਤੇ ਹਰੇਕ ਆਯਾਮ ਵਿੱਚ ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਮੈਟ੍ਰਿਕਸ ਨਾਲੋਂ ਦੁੱਗਣਾ ਵੱਡਾ ਹੁੰਦਾ ਹੈ। ਸੰਖੇਪ ਵਿੱਚ, 3D EM ਤੋਂ ਟ੍ਰਾਂਸਮਿਸ਼ਨ/ਸਕੈਟਰਿੰਗ ਮੈਟ੍ਰਿਕਸ ਸਿਮੂਲੇਸ਼ਨ ਤੱਕ, ਸਿਮੂਲੇਸ਼ਨ ਦੀ ਹਰੇਕ ਪਰਤ ਗਤੀ ਅਤੇ ਸ਼ੁੱਧਤਾ ਦੇ ਵਿਚਕਾਰ ਇੱਕ ਵਪਾਰ-ਬੰਦ ਪੇਸ਼ ਕਰਦੀ ਹੈ, ਅਤੇ ਡਿਜ਼ਾਈਨਰ ਡਿਜ਼ਾਈਨ ਪ੍ਰਮਾਣਿਕਤਾ ਪ੍ਰਕਿਰਿਆ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਉਣ ਲਈ ਆਪਣੀਆਂ ਖਾਸ ਜ਼ਰੂਰਤਾਂ ਲਈ ਸਿਮੂਲੇਸ਼ਨ ਦਾ ਸਹੀ ਪੱਧਰ ਚੁਣਦੇ ਹਨ।

ਹਾਲਾਂਕਿ, ਕੁਝ ਤੱਤਾਂ ਦੇ ਇਲੈਕਟ੍ਰੋਮੈਗਨੈਟਿਕ ਸਿਮੂਲੇਸ਼ਨ 'ਤੇ ਨਿਰਭਰ ਕਰਨਾ ਅਤੇ ਪੂਰੇ PIC ਦੀ ਨਕਲ ਕਰਨ ਲਈ ਇੱਕ ਸਕੈਟਰਿੰਗ/ਟ੍ਰਾਂਸਫਰ ਮੈਟ੍ਰਿਕਸ ਦੀ ਵਰਤੋਂ ਕਰਨਾ ਫਲੋ ਪਲੇਟ ਦੇ ਸਾਹਮਣੇ ਇੱਕ ਪੂਰੀ ਤਰ੍ਹਾਂ ਸਹੀ ਡਿਜ਼ਾਈਨ ਦੀ ਗਰੰਟੀ ਨਹੀਂ ਦਿੰਦਾ ਹੈ। ਉਦਾਹਰਨ ਲਈ, ਗਲਤ ਗਣਨਾ ਕੀਤੀ ਗਈ ਮਾਰਗ ਲੰਬਾਈ, ਮਲਟੀਮੋਡ ਵੇਵਗਾਈਡ ਜੋ ਉੱਚ-ਕ੍ਰਮ ਮੋਡਾਂ ਨੂੰ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਢੰਗ ਨਾਲ ਦਬਾਉਣ ਵਿੱਚ ਅਸਫਲ ਰਹਿੰਦੇ ਹਨ, ਜਾਂ ਦੋ ਵੇਵਗਾਈਡ ਜੋ ਇੱਕ ਦੂਜੇ ਦੇ ਬਹੁਤ ਨੇੜੇ ਹਨ, ਅਣਕਿਆਸੇ ਜੋੜਨ ਦੀਆਂ ਸਮੱਸਿਆਵਾਂ ਵੱਲ ਲੈ ਜਾਂਦੇ ਹਨ, ਸਿਮੂਲੇਸ਼ਨ ਦੌਰਾਨ ਅਣਪਛਾਤੇ ਰਹਿਣ ਦੀ ਸੰਭਾਵਨਾ ਹੈ। ਇਸ ਲਈ, ਹਾਲਾਂਕਿ ਉੱਨਤ ਸਿਮੂਲੇਸ਼ਨ ਟੂਲ ਸ਼ਕਤੀਸ਼ਾਲੀ ਡਿਜ਼ਾਈਨ ਪ੍ਰਮਾਣਿਕਤਾ ਸਮਰੱਥਾਵਾਂ ਪ੍ਰਦਾਨ ਕਰਦੇ ਹਨ, ਫਿਰ ਵੀ ਡਿਜ਼ਾਈਨ ਦੀ ਸ਼ੁੱਧਤਾ ਅਤੇ ਭਰੋਸੇਯੋਗਤਾ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਣ ਅਤੇ ਫਲੋ ਸ਼ੀਟ ਦੇ ਜੋਖਮ ਨੂੰ ਘਟਾਉਣ ਲਈ, ਡਿਜ਼ਾਈਨਰ ਦੁਆਰਾ ਵਿਹਾਰਕ ਅਨੁਭਵ ਅਤੇ ਤਕਨੀਕੀ ਗਿਆਨ ਦੇ ਨਾਲ ਉੱਚ ਪੱਧਰੀ ਚੌਕਸੀ ਅਤੇ ਧਿਆਨ ਨਾਲ ਨਿਰੀਖਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

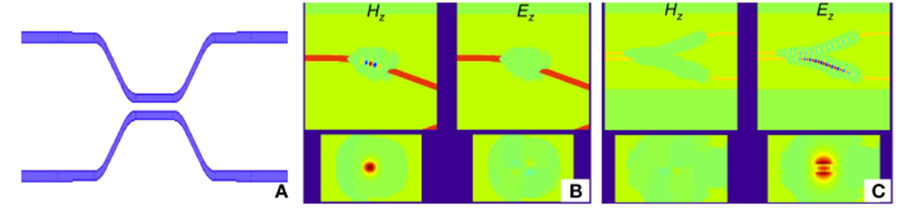

ਸਪਾਰਸ FDTD ਨਾਮਕ ਇੱਕ ਤਕਨੀਕ 3D ਅਤੇ 2D FDTD ਸਿਮੂਲੇਸ਼ਨਾਂ ਨੂੰ ਇੱਕ ਪੂਰੇ PIC ਡਿਜ਼ਾਈਨ 'ਤੇ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਕਰਨ ਦੀ ਆਗਿਆ ਦਿੰਦੀ ਹੈ ਤਾਂ ਜੋ ਡਿਜ਼ਾਈਨ ਨੂੰ ਪ੍ਰਮਾਣਿਤ ਕੀਤਾ ਜਾ ਸਕੇ। ਹਾਲਾਂਕਿ ਕਿਸੇ ਵੀ ਇਲੈਕਟ੍ਰੋਮੈਗਨੈਟਿਕ ਸਿਮੂਲੇਸ਼ਨ ਟੂਲ ਲਈ ਇੱਕ ਬਹੁਤ ਵੱਡੇ ਪੈਮਾਨੇ ਦੇ PIC ਦੀ ਨਕਲ ਕਰਨਾ ਮੁਸ਼ਕਲ ਹੈ, ਸਪਾਰਸ FDTD ਇੱਕ ਕਾਫ਼ੀ ਵੱਡੇ ਸਥਾਨਕ ਖੇਤਰ ਦੀ ਨਕਲ ਕਰਨ ਦੇ ਯੋਗ ਹੈ। ਰਵਾਇਤੀ 3D FDTD ਵਿੱਚ, ਸਿਮੂਲੇਸ਼ਨ ਇੱਕ ਖਾਸ ਮਾਤਰਾ ਵਾਲੇ ਵਾਲੀਅਮ ਦੇ ਅੰਦਰ ਇਲੈਕਟ੍ਰੋਮੈਗਨੈਟਿਕ ਫੀਲਡ ਦੇ ਛੇ ਹਿੱਸਿਆਂ ਨੂੰ ਸ਼ੁਰੂ ਕਰਕੇ ਸ਼ੁਰੂ ਹੁੰਦਾ ਹੈ। ਜਿਵੇਂ ਜਿਵੇਂ ਸਮਾਂ ਵਧਦਾ ਹੈ, ਵਾਲੀਅਮ ਵਿੱਚ ਨਵੇਂ ਫੀਲਡ ਕੰਪੋਨੈਂਟ ਦੀ ਗਣਨਾ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਇਸ ਤਰ੍ਹਾਂ ਹੀ। ਹਰੇਕ ਕਦਮ ਲਈ ਬਹੁਤ ਸਾਰੀ ਗਣਨਾ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਇਸ ਲਈ ਇਸ ਵਿੱਚ ਲੰਮਾ ਸਮਾਂ ਲੱਗਦਾ ਹੈ। ਸਪਾਰਸ 3D FDTD ਵਿੱਚ, ਵਾਲੀਅਮ ਦੇ ਹਰੇਕ ਬਿੰਦੂ 'ਤੇ ਹਰੇਕ ਕਦਮ 'ਤੇ ਗਣਨਾ ਕਰਨ ਦੀ ਬਜਾਏ, ਫੀਲਡ ਕੰਪੋਨੈਂਟਸ ਦੀ ਇੱਕ ਸੂਚੀ ਬਣਾਈ ਰੱਖੀ ਜਾਂਦੀ ਹੈ ਜੋ ਸਿਧਾਂਤਕ ਤੌਰ 'ਤੇ ਇੱਕ ਮਨਮਾਨੇ ਤੌਰ 'ਤੇ ਵੱਡੇ ਵਾਲੀਅਮ ਨਾਲ ਮੇਲ ਖਾਂਦੀ ਹੈ ਅਤੇ ਸਿਰਫ ਉਨ੍ਹਾਂ ਹਿੱਸਿਆਂ ਲਈ ਹੀ ਗਣਨਾ ਕੀਤੀ ਜਾ ਸਕਦੀ ਹੈ। ਹਰੇਕ ਸਮੇਂ ਦੇ ਕਦਮ 'ਤੇ, ਫੀਲਡ ਕੰਪੋਨੈਂਟਸ ਦੇ ਨਾਲ ਲੱਗਦੇ ਬਿੰਦੂ ਜੋੜੇ ਜਾਂਦੇ ਹਨ, ਜਦੋਂ ਕਿ ਇੱਕ ਖਾਸ ਪਾਵਰ ਥ੍ਰੈਸ਼ਹੋਲਡ ਤੋਂ ਹੇਠਾਂ ਫੀਲਡ ਕੰਪੋਨੈਂਟਸ ਛੱਡ ਦਿੱਤੇ ਜਾਂਦੇ ਹਨ। ਕੁਝ ਢਾਂਚਿਆਂ ਲਈ, ਇਹ ਗਣਨਾ ਰਵਾਇਤੀ 3D FDTD ਨਾਲੋਂ ਤੇਜ਼ ਤੀਬਰਤਾ ਦੇ ਕਈ ਆਰਡਰ ਹੋ ਸਕਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਸਪਾਰਸ FDTDS ਫੈਲਾਉਣ ਵਾਲੀਆਂ ਬਣਤਰਾਂ ਨਾਲ ਨਜਿੱਠਣ ਵੇਲੇ ਵਧੀਆ ਪ੍ਰਦਰਸ਼ਨ ਨਹੀਂ ਕਰਦੇ ਕਿਉਂਕਿ ਇਸ ਵਾਰ ਖੇਤਰ ਬਹੁਤ ਜ਼ਿਆਦਾ ਫੈਲਦਾ ਹੈ, ਨਤੀਜੇ ਵਜੋਂ ਸੂਚੀਆਂ ਬਹੁਤ ਲੰਬੀਆਂ ਅਤੇ ਪ੍ਰਬੰਧਨ ਵਿੱਚ ਮੁਸ਼ਕਲ ਹੁੰਦੀਆਂ ਹਨ। ਚਿੱਤਰ 1 ਇੱਕ ਪੋਲਰਾਈਜ਼ੇਸ਼ਨ ਬੀਮ ਸਪਲਿਟਰ (PBS) ਦੇ ਸਮਾਨ 3D FDTD ਸਿਮੂਲੇਸ਼ਨ ਦਾ ਇੱਕ ਉਦਾਹਰਣ ਸਕ੍ਰੀਨਸ਼ਾਟ ਦਿਖਾਉਂਦਾ ਹੈ।

ਚਿੱਤਰ 1: 3D ਸਪਾਰਸ FDTD ਤੋਂ ਸਿਮੂਲੇਸ਼ਨ ਨਤੀਜੇ। (A) ਸਿਮੂਲੇਟ ਕੀਤੇ ਜਾ ਰਹੇ ਢਾਂਚੇ ਦਾ ਇੱਕ ਸਿਖਰਲਾ ਦ੍ਰਿਸ਼ ਹੈ, ਜੋ ਕਿ ਇੱਕ ਦਿਸ਼ਾਤਮਕ ਕਪਲਰ ਹੈ। (B) ਅਰਧ-TE ਐਕਸਾਈਟੇਸ਼ਨ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਇੱਕ ਸਿਮੂਲੇਸ਼ਨ ਦਾ ਇੱਕ ਸਕ੍ਰੀਨਸ਼ੌਟ ਦਿਖਾਉਂਦਾ ਹੈ। ਉੱਪਰ ਦਿੱਤੇ ਦੋ ਚਿੱਤਰ ਅਰਧ-TE ਅਤੇ ਅਰਧ-TM ਸਿਗਨਲਾਂ ਦੇ ਸਿਖਰਲੇ ਦ੍ਰਿਸ਼ ਨੂੰ ਦਿਖਾਉਂਦੇ ਹਨ, ਅਤੇ ਹੇਠਾਂ ਦਿੱਤੇ ਦੋ ਚਿੱਤਰ ਸੰਬੰਧਿਤ ਕਰਾਸ-ਸੈਕਸ਼ਨਲ ਦ੍ਰਿਸ਼ ਨੂੰ ਦਿਖਾਉਂਦੇ ਹਨ। (C) ਅਰਧ-TM ਐਕਸਾਈਟੇਸ਼ਨ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਇੱਕ ਸਿਮੂਲੇਸ਼ਨ ਦਾ ਇੱਕ ਸਕ੍ਰੀਨਸ਼ੌਟ ਦਿਖਾਉਂਦਾ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਜੁਲਾਈ-23-2024