ਉੱਚ-ਸ਼ਕਤੀ ਵਾਲਾ ਪਲਸਡ ਲੇਜ਼ਰਆਲ-ਫਾਈਬਰ MOPA ਢਾਂਚੇ ਦੇ ਨਾਲ

ਫਾਈਬਰ ਲੇਜ਼ਰਾਂ ਦੀਆਂ ਮੁੱਖ ਢਾਂਚਾਗਤ ਕਿਸਮਾਂ ਵਿੱਚ ਸਿੰਗਲ ਰੈਜ਼ੋਨੇਟਰ, ਬੀਮ ਕੰਬੀਨੇਸ਼ਨ ਅਤੇ ਮਾਸਟਰ ਓਸੀਲੇਟਿੰਗ ਪਾਵਰ ਐਂਪਲੀਫਾਇਰ (MOPA) ਢਾਂਚੇ ਸ਼ਾਮਲ ਹਨ। ਇਹਨਾਂ ਵਿੱਚੋਂ, MOPA ਢਾਂਚਾ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਪ੍ਰਾਪਤ ਕਰਨ ਦੀ ਯੋਗਤਾ ਦੇ ਕਾਰਨ ਮੌਜੂਦਾ ਖੋਜ ਹੌਟਸਪੌਟਾਂ ਵਿੱਚੋਂ ਇੱਕ ਬਣ ਗਿਆ ਹੈ।ਪਲਸਡ ਲੇਜ਼ਰਐਡਜਸਟੇਬਲ ਪਲਸ ਚੌੜਾਈ ਅਤੇ ਦੁਹਰਾਓ ਬਾਰੰਬਾਰਤਾ ਦੇ ਨਾਲ ਆਉਟਪੁੱਟ (ਪਲਸ ਚੌੜਾਈ ਅਤੇ ਦੁਹਰਾਓ ਬਾਰੰਬਾਰਤਾ ਵਜੋਂ ਜਾਣਿਆ ਜਾਂਦਾ ਹੈ)।

MOPA ਲੇਜ਼ਰ ਦਾ ਕੰਮ ਕਰਨ ਦਾ ਸਿਧਾਂਤ ਇਸ ਪ੍ਰਕਾਰ ਹੈ: ਮੁੱਖ ਔਸਿਲੇਟਰ (MO) ਇੱਕ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਵਾਲਾ ਬੀਜ ਸਰੋਤ ਹੈਸੈਮੀਕੰਡਕਟਰ ਲੇਜ਼ਰਜੋ ਸਿੱਧੇ ਪਲਸ ਮੋਡੂਲੇਸ਼ਨ ਰਾਹੀਂ ਐਡਜਸਟੇਬਲ ਪੈਰਾਮੀਟਰਾਂ ਦੇ ਨਾਲ ਬੀਜ ਸਿਗਨਲ ਲਾਈਟ ਪੈਦਾ ਕਰਦਾ ਹੈ। ਫੀਲਡ ਪ੍ਰੋਗਰਾਮੇਬਲ ਗੇਟ ਐਰੇ (FPGA) ਮੁੱਖ ਕੰਟਰੋਲ ਐਡਜਸਟੇਬਲ ਪੈਰਾਮੀਟਰਾਂ ਦੇ ਨਾਲ ਪਲਸ ਕਰੰਟ ਸਿਗਨਲਾਂ ਨੂੰ ਆਉਟਪੁੱਟ ਕਰਦਾ ਹੈ, ਜੋ ਕਿ ਡਰਾਈਵ ਸਰਕਟ ਦੁਆਰਾ ਬੀਜ ਸਰੋਤ ਨੂੰ ਚਲਾਉਣ ਅਤੇ ਬੀਜ ਰੌਸ਼ਨੀ ਦੇ ਸ਼ੁਰੂਆਤੀ ਮੋਡੂਲੇਸ਼ਨ ਨੂੰ ਪੂਰਾ ਕਰਨ ਲਈ ਨਿਯੰਤਰਿਤ ਕੀਤੇ ਜਾਂਦੇ ਹਨ। FPGA ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ ਤੋਂ ਨਿਯੰਤਰਣ ਨਿਰਦੇਸ਼ ਪ੍ਰਾਪਤ ਕਰਨ ਤੋਂ ਬਾਅਦ, ਪੰਪ ਸਰੋਤ ਡਰਾਈਵ ਸਰਕਟ ਪੰਪ ਰੋਸ਼ਨੀ ਪੈਦਾ ਕਰਨ ਲਈ ਪੰਪ ਸਰੋਤ ਨੂੰ ਸ਼ੁਰੂ ਕਰਦਾ ਹੈ। ਬੀਜ ਰੌਸ਼ਨੀ ਅਤੇ ਪੰਪ ਰੌਸ਼ਨੀ ਨੂੰ ਬੀਮ ਸਪਲਿਟਰ ਦੁਆਰਾ ਜੋੜਨ ਤੋਂ ਬਾਅਦ, ਉਹਨਾਂ ਨੂੰ ਕ੍ਰਮਵਾਰ ਦੋ-ਪੜਾਅ ਆਪਟੀਕਲ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਮੋਡੀਊਲ ਵਿੱਚ Yb3+ -ਡੋਪਡ ਡਬਲ-ਕਲੈਡ ਆਪਟੀਕਲ ਫਾਈਬਰ (YDDCF) ਵਿੱਚ ਇੰਜੈਕਟ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਇਸ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, Yb3+ ਆਇਨ ਇੱਕ ਆਬਾਦੀ ਉਲਟ ਵੰਡ ਬਣਾਉਣ ਲਈ ਪੰਪ ਰੌਸ਼ਨੀ ਦੀ ਊਰਜਾ ਨੂੰ ਸੋਖ ਲੈਂਦੇ ਹਨ। ਇਸ ਤੋਂ ਬਾਅਦ, ਯਾਤਰਾ ਤਰੰਗ ਪ੍ਰਸਾਰ ਅਤੇ ਉਤੇਜਿਤ ਨਿਕਾਸ ਦੇ ਸਿਧਾਂਤਾਂ ਦੇ ਅਧਾਰ ਤੇ, ਬੀਜ ਸਿਗਨਲ ਲਾਈਟ ਦੋ-ਪੜਾਅ ਆਪਟੀਕਲ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਮੋਡੀਊਲ ਵਿੱਚ ਉੱਚ ਸ਼ਕਤੀ ਲਾਭ ਪ੍ਰਾਪਤ ਕਰਦੀ ਹੈ, ਅੰਤ ਵਿੱਚ ਇੱਕ ਉੱਚ-ਪਾਵਰ ਆਉਟਪੁੱਟ ਕਰਦੀ ਹੈ।ਨੈਨੋਸੈਕਿੰਡ ਪਲਸਡ ਲੇਜ਼ਰ. ਪੀਕ ਪਾਵਰ ਵਿੱਚ ਵਾਧੇ ਦੇ ਕਾਰਨ, ਗੇਨ ਕਲੈਂਪਿੰਗ ਪ੍ਰਭਾਵ ਦੇ ਕਾਰਨ ਐਂਪਲੀਫਾਈਡ ਪਲਸ ਸਿਗਨਲ ਪਲਸ ਚੌੜਾਈ ਸੰਕੁਚਨ ਦਾ ਅਨੁਭਵ ਕਰ ਸਕਦਾ ਹੈ। ਵਿਹਾਰਕ ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ, ਆਉਟਪੁੱਟ ਪਾਵਰ ਨੂੰ ਹੋਰ ਵਧਾਉਣ ਅਤੇ ਕੁਸ਼ਲਤਾ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਅਕਸਰ ਮਲਟੀ-ਸਟੇਜ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਸਟ੍ਰਕਚਰ ਅਪਣਾਏ ਜਾਂਦੇ ਹਨ।

MOPA ਲੇਜ਼ਰ ਸਰਕਟ ਸਿਸਟਮ ਇੱਕ FPGA ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ, ਇੱਕ ਪੰਪ ਸਰੋਤ, ਇੱਕ ਬੀਜ ਸਰੋਤ, ਇੱਕ ਡਰਾਈਵਰ ਸਰਕਟ ਬੋਰਡ, ਇੱਕ ਐਂਪਲੀਫਾਇਰ, ਆਦਿ ਤੋਂ ਬਣਿਆ ਹੁੰਦਾ ਹੈ। FPGA ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ ਬੀਜ ਸਰੋਤ ਨੂੰ MW-ਪੱਧਰ ਦੇ ਕੱਚੇ ਬੀਜ ਲਾਈਟ ਪਲਸਾਂ ਨੂੰ ਐਡਜਸਟੇਬਲ ਪੈਰਾਮੀਟਰਾਂ ਦੇ ਨਾਲ ਆਉਟਪੁੱਟ ਕਰਨ ਲਈ ਚਲਾਉਂਦਾ ਹੈ, ਪਲਸ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਐਡਜਸਟੇਬਲ ਵੇਵਫਾਰਮ, ਪਲਸ ਚੌੜਾਈ (5 ਤੋਂ 200ns), ਅਤੇ ਦੁਹਰਾਓ ਦਰਾਂ (30 ਤੋਂ 900kHz) ਦੇ ਨਾਲ ਤਿਆਰ ਕਰਕੇ। ਇਹ ਸਿਗਨਲ ਪ੍ਰੀਐਂਪਲੀਫਾਇਰ ਅਤੇ ਮੁੱਖ ਐਂਪਲੀਫਾਇਰ ਤੋਂ ਬਣੇ ਦੋ-ਪੜਾਅ ਦੇ ਆਪਟੀਕਲ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਮੋਡੀਊਲ ਵਿੱਚ ਆਈਸੋਲੇਟਰ ਰਾਹੀਂ ਇਨਪੁਟ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਅੰਤ ਵਿੱਚ ਕੋਲੀਮੇਸ਼ਨ ਫੰਕਸ਼ਨ ਦੇ ਨਾਲ ਆਪਟੀਕਲ ਆਈਸੋਲੇਟਰ ਰਾਹੀਂ ਉੱਚ-ਊਰਜਾ ਸ਼ਾਰਟ-ਪਲਸ ਲੇਜ਼ਰ ਨੂੰ ਆਉਟਪੁੱਟ ਕਰਦਾ ਹੈ। ਬੀਜ ਸਰੋਤ ਇੱਕ ਅੰਦਰੂਨੀ ਫੋਟੋਡਿਟੈਕਟਰ ਨਾਲ ਲੈਸ ਹੈ ਜੋ ਅਸਲ ਸਮੇਂ ਵਿੱਚ ਆਉਟਪੁੱਟ ਪਾਵਰ ਦੀ ਨਿਗਰਾਨੀ ਕਰਦਾ ਹੈ ਅਤੇ ਇਸਨੂੰ FPGA ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ ਵਿੱਚ ਵਾਪਸ ਫੀਡ ਕਰਦਾ ਹੈ। ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ ਪੰਪ ਸਰੋਤ 1, 2 ਅਤੇ 3 ਦੇ ਖੁੱਲਣ ਅਤੇ ਬੰਦ ਕਰਨ ਦੇ ਕਾਰਜਾਂ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਪੰਪ ਡਰਾਈਵ ਸਰਕਟ 1 ਅਤੇ 2 ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਦਾ ਹੈ। ਜਦੋਂਫੋਟੋਡਿਟੈਕਟਰਸਿਗਨਲ ਲਾਈਟ ਆਉਟਪੁੱਟ ਦਾ ਪਤਾ ਲਗਾਉਣ ਵਿੱਚ ਅਸਫਲ ਰਹਿਣ 'ਤੇ, ਮੁੱਖ ਕੰਟਰੋਲ ਬੋਰਡ ਸੀਡ ਲਾਈਟ ਇਨਪੁੱਟ ਦੀ ਘਾਟ ਕਾਰਨ YDDCF ਅਤੇ ਆਪਟੀਕਲ ਡਿਵਾਈਸਾਂ ਨੂੰ ਹੋਣ ਵਾਲੇ ਨੁਕਸਾਨ ਨੂੰ ਰੋਕਣ ਲਈ ਪੰਪ ਸਰੋਤ ਨੂੰ ਬੰਦ ਕਰ ਦੇਵੇਗਾ।

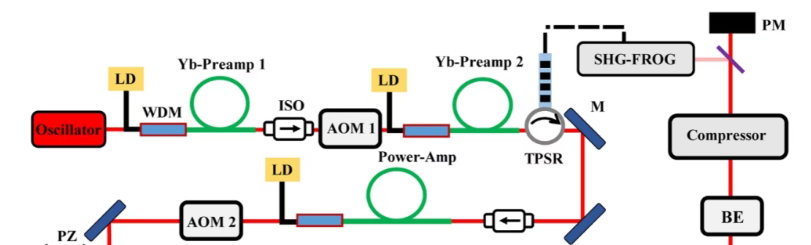

MOPA ਲੇਜ਼ਰ ਆਪਟੀਕਲ ਪਾਥ ਸਿਸਟਮ ਇੱਕ ਆਲ-ਫਾਈਬਰ ਬਣਤਰ ਨੂੰ ਅਪਣਾਉਂਦਾ ਹੈ ਅਤੇ ਇਸ ਵਿੱਚ ਇੱਕ ਮੁੱਖ ਔਸਿਲੇਸ਼ਨ ਮੋਡੀਊਲ ਅਤੇ ਇੱਕ ਦੋ-ਪੜਾਅ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਮੋਡੀਊਲ ਸ਼ਾਮਲ ਹੁੰਦੇ ਹਨ। ਮੁੱਖ ਔਸਿਲੇਸ਼ਨ ਮੋਡੀਊਲ ਇੱਕ ਸੈਮੀਕੰਡਕਟਰ ਲੇਜ਼ਰ ਡਾਇਓਡ (LD) ਨੂੰ ਬੀਜ ਸਰੋਤ ਵਜੋਂ 1064nm ਦੀ ਕੇਂਦਰੀ ਤਰੰਗ-ਲੰਬਾਈ, 3nm ਦੀ ਲਾਈਨਵਿਡਥ, ਅਤੇ 400mW ਦੀ ਵੱਧ ਤੋਂ ਵੱਧ ਨਿਰੰਤਰ ਆਉਟਪੁੱਟ ਪਾਵਰ ਲੈਂਦਾ ਹੈ, ਅਤੇ ਇਸਨੂੰ 99%@1063.94nm ਦੀ ਪ੍ਰਤੀਬਿੰਬਤਾ ਅਤੇ 3.5nm ਦੀ ਲਾਈਨਵਿਡਥ ਦੇ ਨਾਲ ਇੱਕ ਫਾਈਬਰ ਬ੍ਰੈਗ ਗਰੇਟਿੰਗ (FBG) ਨਾਲ ਜੋੜ ਕੇ ਇੱਕ ਵੇਵ-ਲੰਬਾਈ ਚੋਣ ਪ੍ਰਣਾਲੀ ਬਣਾਉਂਦਾ ਹੈ। 2-ਪੜਾਅ ਐਂਪਲੀਫਿਕੇਸ਼ਨ ਮੋਡੀਊਲ ਇੱਕ ਰਿਵਰਸ ਪੰਪ ਡਿਜ਼ਾਈਨ ਨੂੰ ਅਪਣਾਉਂਦਾ ਹੈ, ਅਤੇ 8 ਅਤੇ 30μm ਦੇ ਕੋਰ ਵਿਆਸ ਵਾਲੇ YDDCF ਨੂੰ ਕ੍ਰਮਵਾਰ ਲਾਭ ਮੀਡੀਆ ਵਜੋਂ ਸੰਰਚਿਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਸੰਬੰਧਿਤ ਕੋਟਿੰਗ ਪੰਪ ਸੋਖਣ ਗੁਣਾਂਕ ਕ੍ਰਮਵਾਰ 1.0 ਅਤੇ 2.1dB/m@915nm ਹਨ।

ਪੋਸਟ ਸਮਾਂ: ਸਤੰਬਰ-17-2025